Features and Benefits

- Full-chip performance – combines the performance of the Calibre hierarchical and multi-threaded architecture with a compact netlist to boost throughput of large designs and maintain rapid feedback within custom design environments. Multiple process corner analysis does not require complete design re-run.

- Proven accuracy – Advanced extraction and process models correlate closely with field solver results; proprietary reduction algorithm maintains integrity of parasitic data. Reduces need for prohibitive design margins by ncorporating manufacturing dependent effects (e.g., in-die variation) into parasitic models.

- Rule deck availability – Availability of foundry-certified signoff rule decks in SVRF format ensures Calibre xRC parasitic extraction can meet your design needs regardless of process or foundry choice.

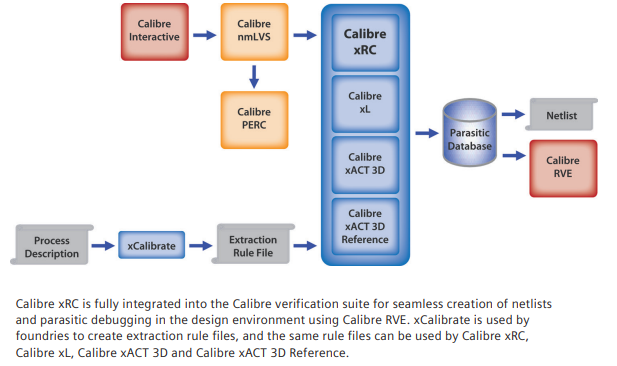

- Easy flow integration – Calibre xRC exchanges native database information with Calibre nmLVS, Calibre PERC, and Calibre xACT 3D products. Upstream design integration using Calibre Interactive, Calibre View and Calibre RVE enables GUI-driven launch, back annotation, and cross-probing for all popular layout environments.

- Support for all major transistor based and cell-based simulation and analysis netlist formats ensures compatibility with downstream digital, custom, and mixed-signal flows.