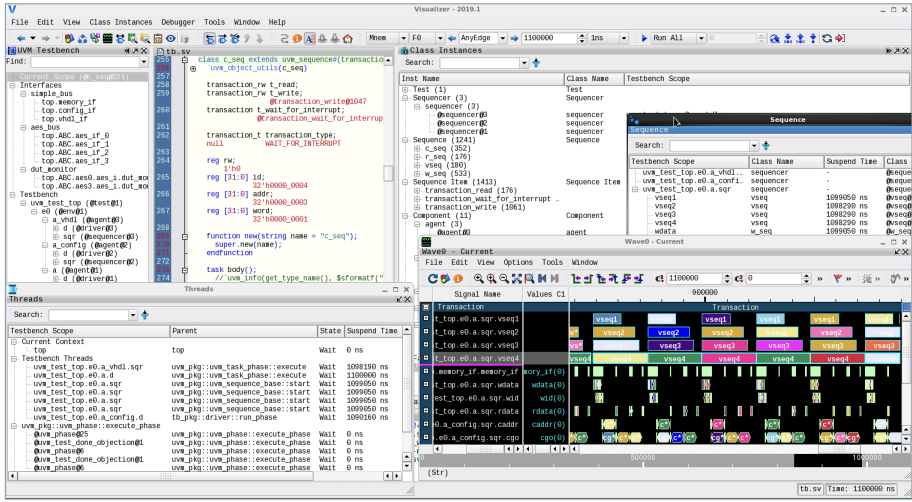

Features and Benefits:

- Support for a variety of languages: Visualizer supports a variety of languages, including Verilog, VHDL, and SystemVerilog. This can help designers to debug a variety of designs.

- High performance: Visualizer can debug designs of any size, from small blocks to large chips. This can help designers to achieve faster time to market.

- High accuracy: Visualizer uses a variety of techniques to ensure that the results of the debugging are accurate. This can help designers to achieve improved quality.

- Scalability: Visualizer can scale to handle large designs. This can help designers to debug complex designs.

- Integration: Visualizer can be integrated with a variety of other tools, such as simulators, emulators, and physical synthesis tools.

- Faster time to market: Visualizer can help designers to achieve faster time to market by providing them with a comprehensive set of features that can help them to debug their designs quickly and accurately.

- Improved quality: Visualizer can help designers to improve the quality of their designs by providing them with a comprehensive set of features that can help them to identify and fix design flaws early in the design process.

- Lower cost of debug: Visualizer can help designers to reduce the cost of debug by providing them with a comprehensive set of features that can help them to debug their designs efficiently.

- Increased confidence: Visualizer can help designers to increase their confidence in their designs by providing them with a comprehensive set of features that can help them to verify the correctness of their designs.

- Visualizer supports a variety of technologies, including CMOS, BiCMOS, and RF.

- Visualizer can be used to debug a variety of designs, including chips, modules, and systems.

- Visualizer is available as a stand-alone tool or as an integrated part of the Siemens EDA suite.