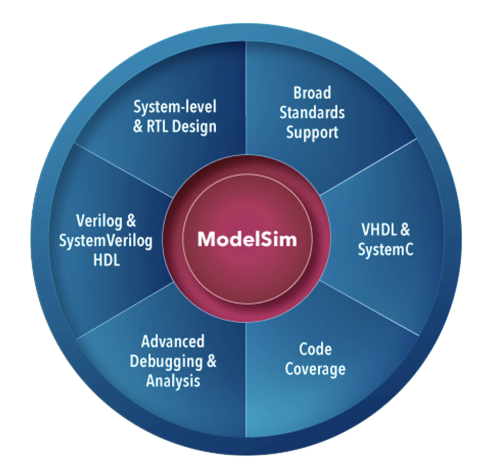

Features and Benefits:

- Language Support: ModelSim supports industry-standard HDL languages, including VHDL, Verilog, and SystemVerilog. It allows designers to work with their preferred language to describe and simulate digital and mixed-signal designs.

- Behavioral and Gate-Level Simulation: ModelSim offers both behavioral and gate-level simulation capabilities. Behavioral simulation allows designers to simulate and test high-level descriptions of their designs, while gate-level simulation enables detailed analysis of the synthesized and optimized gate-level netlists.

- Interactive Debugging: The tool provides an interactive debugging environment, allowing designers to trace signals, view waveforms, inspect internal registers, and set breakpoints during simulation. This helps in identifying and diagnosing issues efficiently.

- Waveform Viewer: ModelSim includes a waveform viewer that displays simulation results graphically. Designers can analyze signal behavior over time, examine digital waveforms, and zoom in on specific regions of interest.

- Testbench Support: ModelSim supports testbenches, which are essential for verifying designs through simulation. Designers can create and use testbenches to apply stimulus to the design and evaluate its responses.

- Coverage Analysis: The tool offers coverage analysis features to assess the completeness of the testbench and identify untested areas of the design. It helps in achieving thorough test coverage and verifying design correctness.

- Performance Optimization: ModelSim is optimized for performance and can efficiently simulate large and complex designs. It leverages multithreading and other advanced techniques to speed up simulations and reduce verification time.

- SystemVerilog Assertions (SVA): The tool supports SystemVerilog Assertions (SVA), enabling designers to define and apply formal verification properties to the design for more rigorous verification and bug detection.

- Code Coverage Analysis: ModelSim includes code coverage analysis capabilities, which allow designers to track how much of the RTL code has been exercised during simulation. It helps in evaluating the completeness of the verification process.

- Co-simulation with Third-Party Tools: ModelSim can be seamlessly integrated with third-party tools and simulators, enabling co-simulation with other verification environments and verification methodologies.